Delta 35 Specifications Page 4

- Page / 18

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

AN217

4 Rev. 0.2

2.2.1. Voltage Reference

The voltage reference circuit should be treated as carefully as the measured signal, because noise on the voltage

reference degrades ADC performance. The C8051F35x can use its on-chip voltage reference (2.4 V typical) or an

externally supplied voltage reference (input to the VREF+ and VREF– pins). For optimal performance, we

recommend the use of a high-quality, low-noise external reference. To filter noise, use a 1.0 µF ceramic capacitor

connected between VREF+ and VREF–, placed as close to the pins as possible.

Note: When using the internal voltage reference, VREF– must be connected to ground externally. This is typically done by con-

necting the VREF– pin directly to the analog ground plane.

2.2.2. Programmable Gain

The goal is to match the input signal dynamic range to the dynamic range that can be measured by the ADC

(based on voltage reference voltage). This can be accomplished by scaling the voltage reference (VREF) voltage

and by amplifying the signal. A larger VREF voltage improves performance, thus it is better to apply gain to the

signal rather than reducing VREF. A signal can be amplified using a combination of an external amplifier and/or the

internal programmable gain amplifier. (See “2.1.4. External Buffer and Gain” on page 2.)

The C8051F35x devices feature an on-chip programmable gain amplifier (PGA) with eight gain settings. The ADC

input gain is selected using the ADC0 Control Register (ADC0CN). ADC0CN[2:0] are the AD0GN bits used to

select one of the eight gain settings. (See SFR Definition 2.1.)

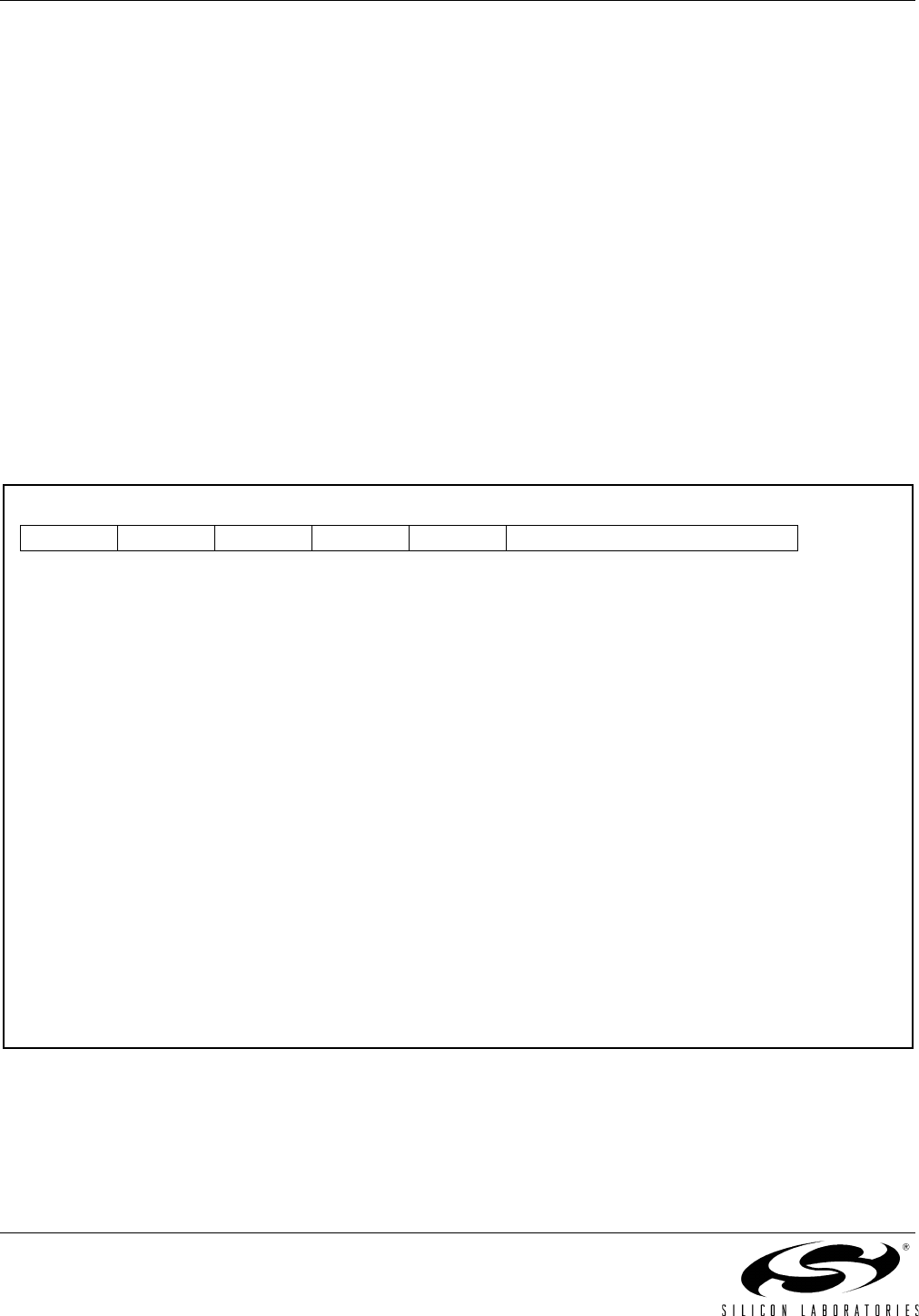

SFR Definition 2.1. ADC0CN: ADC0 Control Register

Bits 7–5: Unused: Read = 000b, Write = don’t care.

Bit 4: AD0POL: ADC0 Polarity.

0: ADC operates in Unipolar mode (straight binary result).

1: ADC operates in Bipolar mode (2s compliment result).

Bit 3: AD0BCE: ADC0 Burnout Current Source Enable.

0: ADC Burnout current sources disabled.

1: ADC Burnout current sources enabled.

Bits 2:0 AD0GN: ADC0 Programmable Gain Setting.

000: PGA Gain = 1.

001: PGA Gain = 2.

010: PGA Gain = 4.

011: PGA Gain = 8.

100: PGA Gain = 16.

101: PGA Gain = 32.

110: PGA Gain = 64.

111: PGA Gain = 128.

This SFR can only be modified when ADC0 is in IDLE mode.

R R R R/W R/W R/W R/W R/W Reset Value

- - - AD0POL AD0BCE AD0GN 00010000

Bit7 Bit6 Bit5 Bit4 Bit3 Bit2 Bit1 Bit0

SFR Address:

0xF4

- 1. Introduction 1

- Relevant Devices 1

- 2.1. Signal 2

- Rev. 0.2 3 3

- ADC0CN: ADC0 Control Register 4

- MDCLK SYSCLK()ADC0CLK 1+()⁄= 5

- 6 Rev. 0.2 6

- DECIMATION RATIO DECI 10:1[]= 7

- 8 Rev. 0.2 8

- Rev. 0.2 9 9

- 010: Single Conversion 10

- 111: System Gain Calibration 10

- 3. Hardware Design 11

- C8051F35x 12

- Number of Samples 13

- ADC Codes 13

- 4.2. Noise-Free Resolution 14

- 4.1. Effective Resolution 14

- Rev. 0.2 15 15

- DOCUMENT CHANGE LIST 16

- Rev. 0.2 17 17

- CONTACT INFORMATION 18

Comments to this Manuals