Delta 45 Specifications Page 31

- Page / 44

- Table of contents

- BOOKMARKS

Rated. / 5. Based on customer reviews

ADC12EU050

www.ti.com

SNAS444I –JANUARY 2008–REVISED APRIL 2013

Bit Description

1 PD1: Power Down Channel 1

0 Channel Active

1 Channel Power Down

0 PD0: Power Down Channel 0

0 Channel Active

1 Channel Power Down

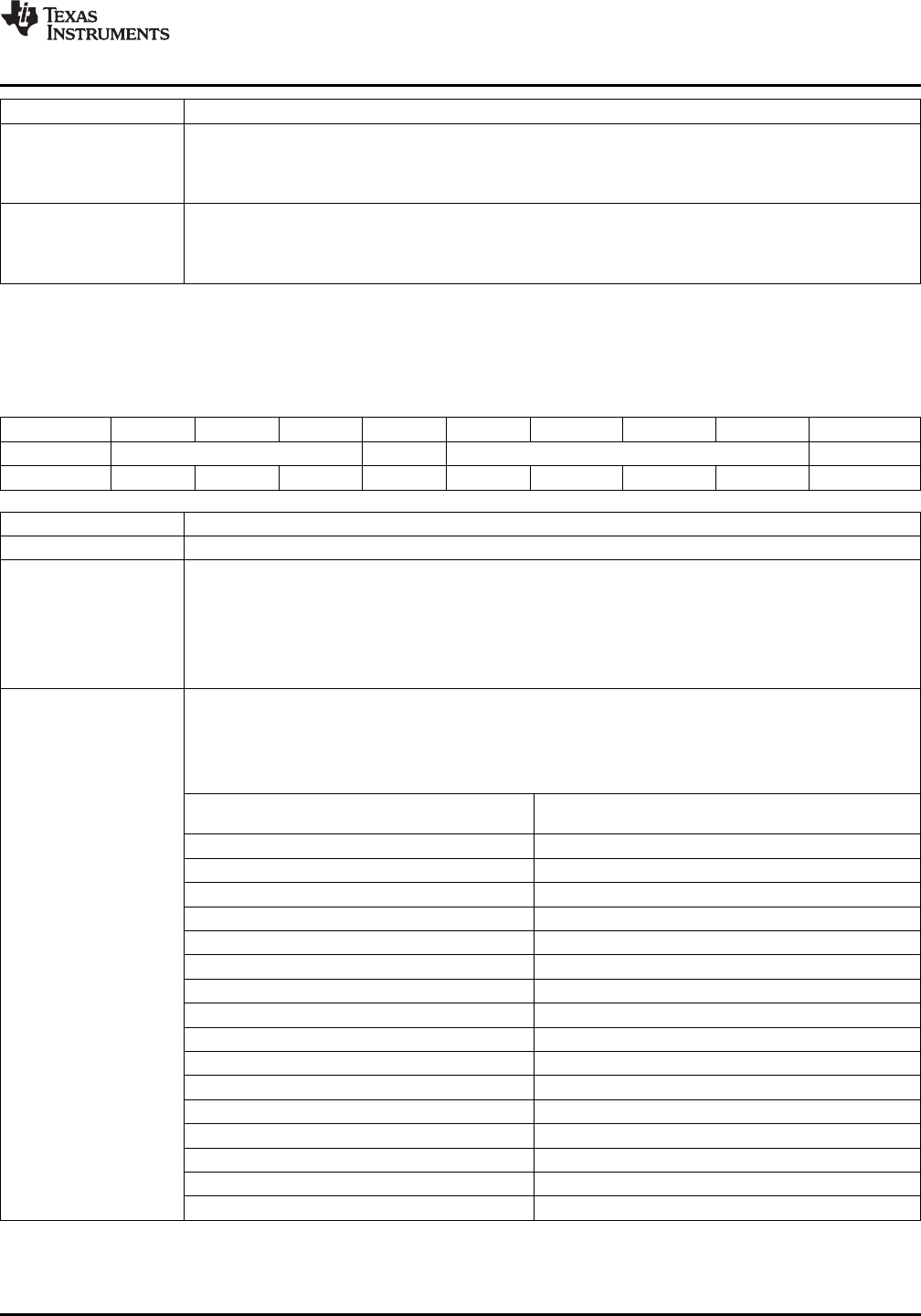

Modulator Overload Control Register

• Address: 04h

• Attributes: Write Only

• Register 05h reads back contents of register 04h

b[7] b[6] b[5] b[4] b[3] b[2] b[1] b[0] HEX

Description Reserved IOR OL[3:0]

Default 0 0 0 0 0 0 0 0 00 h

Bit Description

7:5 Reserved. Write as zero for future compatibility.

4 IOR: Enable IOR Mode (Instant Overload Recovery)

This bit can be used to quickly enable IOR mode with the default IOR settings for DGF (see register 14h) and

OL.

0 IOR Mode Disabled

1 IOR Mode Enabled

3:0 OL[3:0]: The bits define the differential peak voltage (in V

PP

) at which the analog input signal is clipped when

in IOR mode. In IOR mode the analog clipping is set to 1.746 V

PP

. In the default ADC mode clipping of the

analog input signal is disabled.

Should it be decided to over-ride the default setting, it is important to follow the guidelines for setting OL, as

described in APPLICATION INFORMATION.

Clipping Voltage

OL[3:0]

V

PP

0 (IOR Mode default) 1.746

0001 1.694

0010 1.64

0011 1.586

0100 1.534

0101 1.480

0110 1.426

0111 1.374

1000 2.172

1001 2.120

1010 2.066

1011 2.012

1100 1.960

1101 1.906

1110 1.852

1111 1.800

Copyright © 2008–2013, Texas Instruments Incorporated Submit Documentation Feedback 31

Product Folder Links: ADC12EU050

- Converter 1

- ADC12EU050 10

- 32 + 4 x DGFa + DGFb 34

- PACKAGE OPTION ADDENDUM 39

- NKE0068A 41

- IMPORTANT NOTICE 44

(34 pages)

(34 pages) (28 pages)

(28 pages)

Comments to this Manuals